上一篇我们阐述了米勒钳位在SiC驱动中的关键作用。本文将继续深入,解析SiC驱动的短路保护机制,并阐述测试平台搭建的核心要点。尽管短路保护的理论与设计已很成熟,但其真正的价值体现在实际应用的可靠性上。SiC器件具备更快的开关速度与更大的短路电流,这对保护的快速响应与鲁棒性提出了严苛考验。希望本文能为您验证SiC驱动的短路保护功能,提供切实的参考与帮助。

短路保护第一步:检测

实现短路保护的首要步骤,是准确、快速地检测到短路故障。通常,我们将短路分为两类:一类短路(桥臂直通) 与二类短路(负载或相间短路)。在设计中,驱动电路通常能确保对一类短路的可靠保护,但对于二类短路,则往往不会做出明确的承诺。

这背后的原因是什么?核心差异在于故障特性。一类短路发生在同一桥臂内部,回路杂散电感极小,其电流上升率(di/dt)极高,对开关管构成最直接、最严峻的威胁,是保护设计的首要目标和硬性指标。而二类短路路径上的杂散电感较大,电流上升相对缓慢,但其诊断更为复杂,常常需要系统层级的协同保护。

将短路检测方案归类,核心无外乎两种:退饱和检测 与 di/dt检测。

二者的选择,很大程度上取决于功率模块的自身结构。di/dt 检测作为一种更“定制化”的方案,需要模块提供辅助端子或特殊设计作为支撑,这在 EconoDual 等标准化封装中难以实现。相比之下,退饱和检测的通用性更强,因而成为了当下 SiC 驱动保护的绝对主流。其经典电路与工作原理已非常成熟,读者可轻松在网上找到相关资料。

退饱和检测有一个非常重要的前提,就是模块能够进入退饱和的状态。如果把SiC器件看作一个水阀,饱和区相当于阀门开得足够大,水流(电流)的大小完全由水压和水管粗细(外部电路)决定。此时,阀门(SiC器件)本身只承受一个很小的、固定的压降(相当于器件的 Vds(sat) 或 Vds(on))。而退饱和则相当于现在有一个巨大的外力试图推动水流(短路),但你的阀门开度(栅极电压)是固定的。水流太大,以至于阀门两端的压差(Vds(desat))急剧升高,它不再处于那个“低阻、低压降”的状态了。这个压差就是我们检测短路的关键参数。

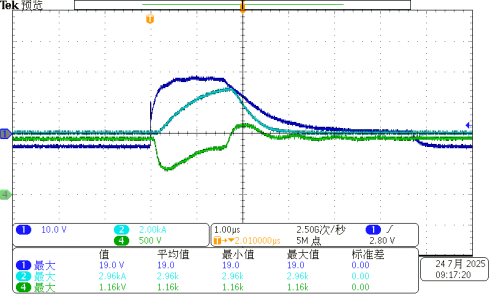

下面是从实际测试当中摘取的波形。我们可以从波形中看到,当模块进入退饱和的状态时,Vds电压在下降到0V之前有一个明显的抬升动作。此时最低点的电压就是上面说到的Vds(desat)。而没有退保和的波形则和正常双脉冲波形类似。

短路保护第二步:执行

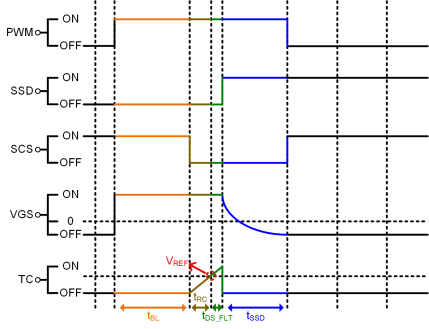

检测到短路后,保护流程随即启动。不同厂家的驱动芯片在信号逻辑上各有不同,下图展示了飞仕得SiC驱动的典型保护序列:

-故障屏蔽期 (消隐时间 tBL):短路发生后,保护并非立即动作,而是先进入一段极短的屏蔽期。此举旨在规避器件开通瞬间可能引起的电流误判,确保可靠性。

-故障判定期 (RC充电时间 tRC):屏蔽期结束后,故障信号通过RC电路充电,当其电压达到设定阈值VREF时,初步确认故障发生。

-故障确认期 (数字滤波 tDS_FLT):为杜绝干扰信号导致的误报,驱动芯片内置的数字滤波器将再次进行延时确认,至此,短路故障被最终锁定。

-安全关断期 (软关断):保护确认后,驱动将执行软关断(采用大电阻关断),平缓降低关断电流,确保模块安全地退出工作状态。

相比于IGBT,SiC的短路保护难点核心在于“快”和“稳”。对比下面两个短路保护过程。我们可以看到:

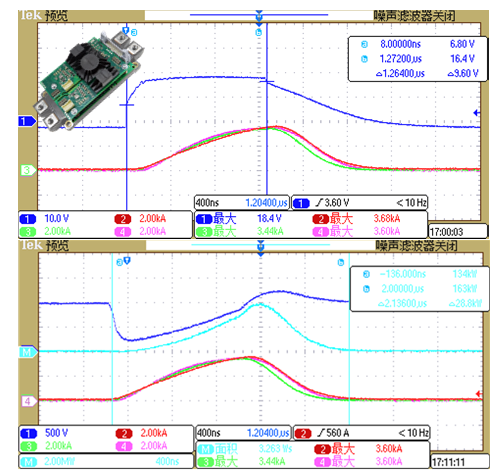

1.SiC的短路保护响应时间(约1.5μs)与完全关断时间(< 3μs)均远短于IGBT(分别为4μs与6-8μs)。这意味着驱动电路必须在极为有限的时间预算内,完成从故障识别到安全关断的全过程。这一改变使得驱动设计的核心,聚焦于滤波时间常数与检测电压阈值的精确协同,任何不当的配置都可能导致保护失效或误动作。

2. 对比IGBT的Vce与SiC MOSFET的Vds在退饱和时的状态,一个关键区别在于:SiC的退饱和电压变化幅度更小。这意味着,用于判断短路的电压“窗口”更窄,使得准确检测变得更为困难。因此,检测电路必须具备更高的精度和分辨能力,其核心设计目标是在不干扰正常工作的前提下,精准捕捉到这一微弱的故障信号。

3. IGBT与SiC的短路电流特性迥异:前者快速进入平台期,后者则在保护窗口内持续线性增长(理论上达到峰值后电流进入衰减阶段,但此时模块已经损坏,没有保护的意义)。这一差异导致SiC在短路期间的能量积累更为显著,因此必须严格关注其短路耐受能量。不同厂商模块的耐受能力差别巨大。

短路保护测试:测试平台

短路保护测试本质上是高风险的。当前SiC模块工艺仍在演进中,其耐受能力存在分散性,使得测试中发生模块失效(即“炸管”) 的概率显著增加。因此,建立一套科学、安全且可控的测试流程至关重要。进行此类测试的首要环节,便是在受控条件下,安全、可靠地模拟出短路故障。

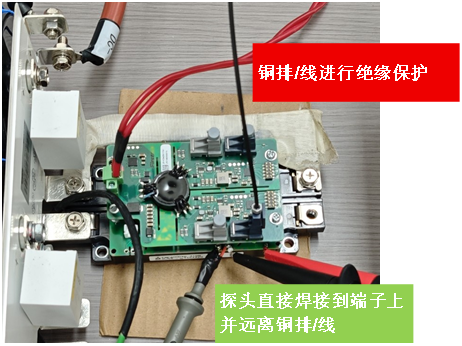

目前常见的短路测试方式主要有使用短接铜排/铜线或者让上下管同开造成桥臂直通。如下图所示的两并联测试平台,母排的DC和AC侧通过铜排进行了短接。在测试过程中切记保持探头和铜排之间的距离,防止铜排上的大电流对探头造成的影响。在实际测试中,我们建议:

1. 对铜排进行绝缘处理,防止不必要的意外

2. 门极探头使用地线环(将探头直接焊接在栅极(G)和源极(S))或者光隔离探头,其他探头在测试时受到干扰的可能性极大

3. 铜排/铜线尽可能短且粗来降低杂感,模拟真实的一类短路环境

除了前述的铜排短接法,另一种高保真的测试方案是驱动上下管同时开通,以模拟最真实的桥臂直通工况。该方法能精准复现一类短路,其核心挑战在于如何生成两个完全同步且精准可控的开通信号。为此,飞仕得自研的实验室动态测试设备ME400D提供了完美的解决方案。它不仅能轻松实现精确的上下管同开控制,更能将短路保护测试与常规双脉冲测试的效率提升至全新高度,实现全流程的自动化测试与智能波形分析。

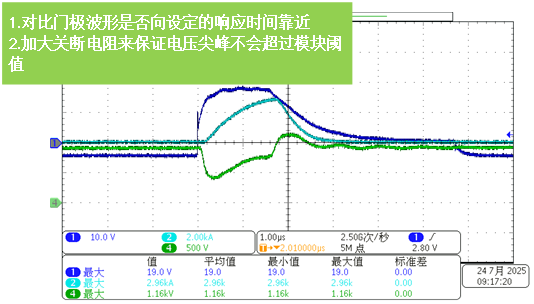

以下波形是我们使用ME400D在内部做的三并联SiC短路测试波形示例。使用的是我们为ED3封装设计的驱动2FHD0620。(蓝色:门极信号(上图),Vds(下图),其余波形为电流)

短路保护测试:测试过程

SiC短路测试与IGBT的一大区别在于可从低压起步。为确保安全,建议的标准化流程是:首先在20V低压下验证系统工作正常;然后从100V开始,以100V为步长逐级升压进行测试;且每次测试后必须保持5-10分钟的间隔,用于模块冷却与系统恢复。如果测试过程中出现炸管或者一些异常,切记第一时间下电,不要带高压操作。

短路保护测试:波形分析

接下来是飞仕得在实际测试中分析波形的一些经验。首先我们仍然以上面提到的波形为例。在短路测试当中,除了大家熟知的电压电流之外,我们还需要关注哪些细节:

1. 并非所有的SiC模块都可以顺利的进入退保和状态。假设我们使用了一个1200V/300A的模块,在测试当中我们经常会遇到到了400V甚至500V都无法退饱和的情况,再往上继续测试如果模块仍然不退饱和风险极大,这个时候我们可以采取两个措施来尽可能保证安全:

1. 对比门极波形:在模块趋近退饱和时,门极波形的持续时间会越来越接近短路保护响应时间,可以通过这个判断模块是否有进入退饱和状态的趋势。

2. 加大关断电阻,由于驱动在检测到退保和之前都是硬关断,只要Vds尖峰不超过模块耐压,整个短路过程的损耗是相对较低的,模块过流损坏的风险较低。这样可以继续抬升母线电压来对模块做摸底测试。

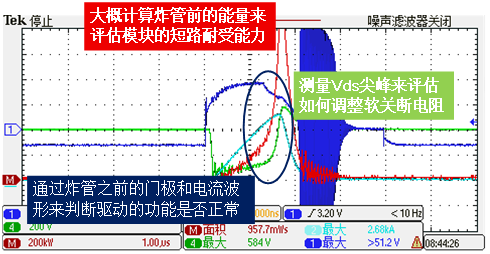

2. 并非每次测试都是顺利的,如果发生炸管,我们也可以从波形中进行一些分析。如下面这个炸管的波形。其中我们需要关注以下几个非常关键的点:

1. 在炸管之前整个短路过程的能量,这可以帮助我们评估模块的短路耐受能力。

2. 炸管时门极和电流是否开始下降,如果下降,则可以间接证明驱动的保护功能正常工作,如果没有,则很有可能驱动的信号收到了干扰。

3. 此时Vds的电压尖峰,这直接决定了我们接下来更改软关断电阻时的选值。更小的软关断电阻可以让关断更快但是也会造成Vds尖峰过高的问题。

3. 为了尽可能详细验证驱动的短路保护能力,多种数据需要进行记录:

测试项目 | 说明 |

VGSMAX(V) | 最大栅极电压 |

VDSMAX(V) | 最大漏源极电压 |

ISD(A) | 最大短路电流 |

PMAX(MW) | 短路时最大功率 |

ESC(J) | 短路时损耗 |

TSC(μs) | 短路时间(门级开通至门级开始关断) |

TOFF(μs) | 关断时间(门级开始软关断-电流为0) |

TSSD(μs) | 软关断时间 |

TSC_PRO(μs) | 短路时间(开通10%电流-关断10%电流) |

短路测试毫无疑问是非常考验勇气的测试,再多理论分析最终还是要在测试台架上进行测试。特别是经历了炸管之后,每一次测试都会提心吊胆。在这里也要向在打短路的各位工程师报以衷心的敬佩!